## Boolean Algebra and Logic Gates

Grade 10 unit 04

LIVEWORKSHEETS

# Introduction.....

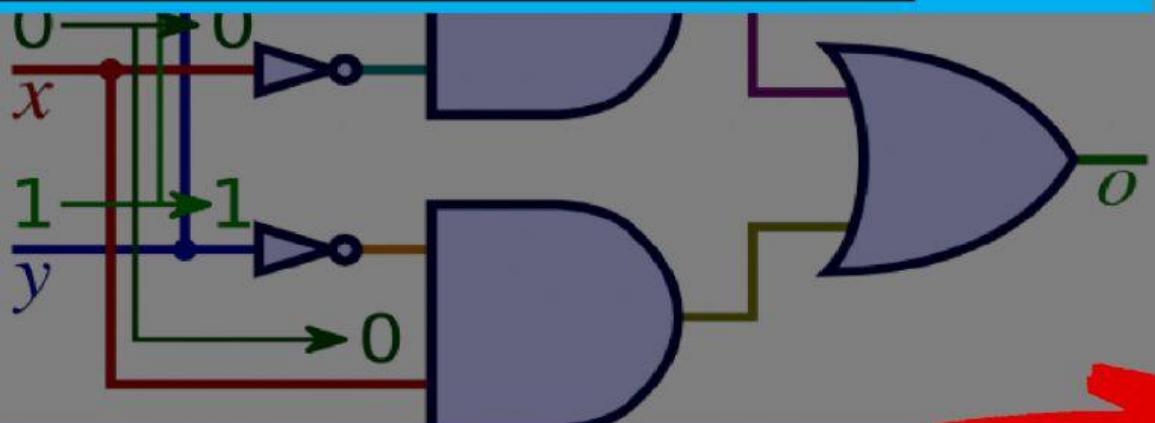

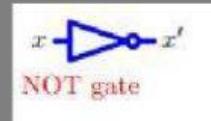

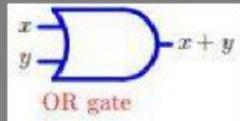

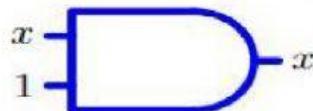

**Logic Gates (Introduction)** The package Truth Tables and Boolean Algebra set out the basic principles of logic. Any Boolean algebra operation can be associated with an electronic circuit in which the inputs and outputs represent the statements of Boolean algebra. Although these circuits may be complex, they may all be constructed from three basic devices. These are the AND gate, the OR gate and the NOT gate.

In the case of logic gates, a different notation is used:  $x \wedge y$ , the logical AND operation, is replaced by  $x \cdot y$ , or  $xy$ .  $x \vee y$ , the logical OR operation, is replaced by  $x + y$ .  $\neg x$ , the logical NEGATION operation, is replaced by  $x 0$  or  $x$ . The truth value TRUE is written as 1 (and corresponds to a high voltage), and FALSE is written as 0 (low voltage).

## 2. Truth Tables

| $x$ | $y$ | $x \cdot y$ |

|-----|-----|-------------|

| 0   | 0   | 0           |

| 0   | 1   | 0           |

| 1   | 0   | 0           |

| 1   | 1   | 1           |

Summary of AND gate

| $x$ | $y$ | $x + y$ |

|-----|-----|---------|

| 0   | 0   | 0       |

| 0   | 1   | 1       |

| 1   | 0   | 1       |

| 1   | 1   | 1       |

Summary of OR gate

| $x$ | $x'$ |

|-----|------|

| 0   | 1    |

| 1   | 0    |

Summary of NOT gate

### 3. Basic Rules of Boolean Algebra

The basic rules for simplifying and combining logic gates are called Boolean algebra in honour of George Boole (1815–1864) who was a self-educated English mathematician who developed many of the key ideas. The following set of exercises will allow you to rediscover the basic rules:

#### Example 1

Consider the **AND** gate where one of the inputs is **1**. By using the truth table, investigate the possible outputs and hence simplify the expression  $x \cdot 1$ .

**Solution** From the truth table for **AND**, we see that if  $x$  is **1** then  $1 \cdot 1 = 1$ , while if  $x$  is **0** then  $0 \cdot 1 = 0$ . This can be summarised in the rule that  $x \cdot 1 = x$ , i.e.,

## Example 2

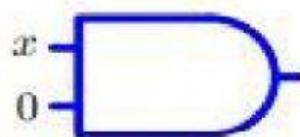

Consider the **AND** gate where one of the inputs is **0**. By using the truth table, investigate the possible outputs and hence simplify the expression  $x \cdot 0$ .

**Solution** From the truth table for **AND**, we see that if  $x$  is **1** then  $1 \cdot 0 = 0$ , while if  $x$  is **0** then  $0 \cdot 0 = 0$ . This can be summarised in the rule that  $x \cdot 0 = 0$

### Let's watch a video clip

LIVEWORKSHEETS

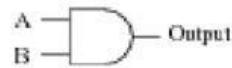

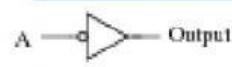

01. Identify each of these logic gates by name, and complete their respective truth tables:

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | Output |

|---|--------|

| 0 |        |

| 1 |        |

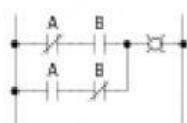

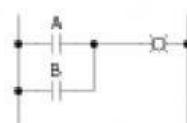

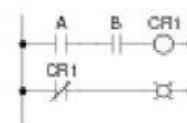

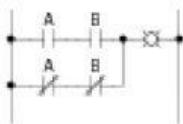

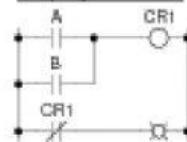

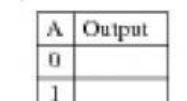

02. Identify each of these relay logic functions by name (AND, OR, NOR, etc.) and complete their respective truth tables:

OR

XOR

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

NAND

XNOR

| A | B | Output |

|---|---|--------|

| 0 | 0 |        |

| 0 | 1 |        |

| 1 | 0 |        |

| 1 | 1 |        |

NOT

NOR

**LIVEWORKSHEETS**